Generator przebiegów arbitralnych

Napisano dnia 11.07.2015 r. o godzinie 15:55

Autor: Piotr Sperka

Wstęp

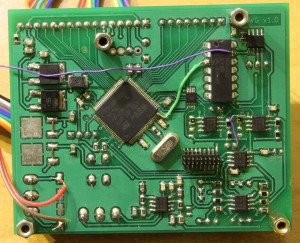

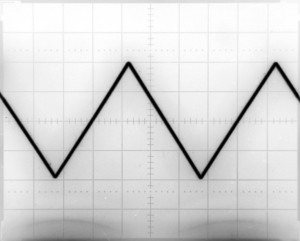

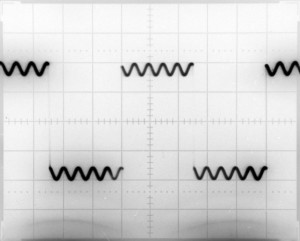

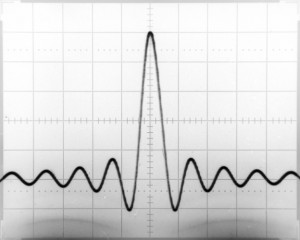

Prezentowany generator przebiegów arbitralnych został zbudowany pomiędzy sierpniem a grudniem 2014 roku, jako projekt inżynierski. Został on oceniony na ocenę bardzo dobrą. Na wstępie muszę zaznaczyć, że jestem całkowicie świadomy pewnych niedoskonałości prezentowanego układu, i gdybym projektował go ponownie, niektóre elementy rozwiązałbym inaczej. Więcej na ten temat napisałem na końcu tego artykułu. Krótki komentarz należy się także parametrom technicznym układu, w szczególności osiąganej częstotliwości maksymalnej. Układ ten projektowany był w założeniach jako generator arbitralny do „odtwarzania” (bardzo) wolno zmiennych przebiegów (w szczególności biomedycznych), a dodatek w postaci generatora przebiegów funkcyjnych (przebiegi: sinusoidalny, trójkątny, piłokształtny, prostokątny) nie był bezpośrednio tematem pracy – stąd też jego bardzo przeciętne parametry częstotliwościowe, podyktowane maksymalną częstotliwością próbkowania zastosowanego przetwornika CA.

Założenia projektowe

Przed zaprojektowaniem układu ustalone zostały założenia dotyczące jego funkcjonalności, które przedstawiłem w poniższych punktach:

- Dwa niezależne kanały.

- Częstotliwość próbkowania 200kHz dla każdego kanału.

- Rozdzielczość sygnału równa 16 bitów.

- Maksymalna amplituda wyjściowa nie mniejsza niż 10V.

- Impedancja wyjściowa 600Ω.

- Cyfrowe ustalanie nastaw amplitudy, składowej stałej, częstotliwości, kształtu przebiegu.

Zastosowane układy

W fazie prototypowania układu wypróbowałem kilka różnych koncepcji układu, żeby w końcu uzyskać sensowny kompromis pomiędzy jakością oraz ceną i poziomem skomplikowania układu. Poniżej przedstawiam listę najważniejszych wykorzystanych do budowy układów scalonych:

- Mikrokontroler z rodziny STM32F2 – STM32F205VCT6

- Główny przetwornik cyfrowo-analogowy AD5663

- Pomocnicze przetworniki cyfrowo-analogowe MCP4922

- Wzmacniacze operacyjne NE5532

Schemat blokowy układu

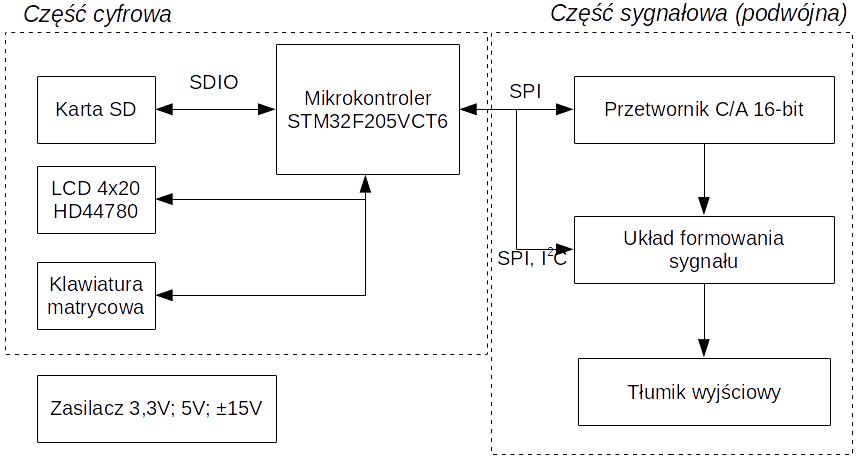

Część cyfrowa

W układzie zastosowano mikrokontroler STM32 pracujący z częstotliwością 120MHz i dysponujący wieloma interfejsami dla peryferiów. Przetwornik AD5663 został przyłączony do magistrali SPI1 pracującej z częstotliwością 30MHz, natomiast przetworniki MCP4922 do magistrali SPI2 pracującej z częstotliwością 15MHz. Karta pamięci jest obsługiwana przy pomocy interfejsu SDIO, aby uzyskać jak największą prędkość przesyłu danych oraz biblioteki FatFS do obsługi systemu plików. Podczas wstępnych testów okazało się, że do zachowania płynności przesyłu danych konieczne jest wykorzystanie DMA. Bez tego nie wystarczało czasu nawet na samo wysyłanie danych do przetwornika CA z częstotliwością próbkowania 100kHz dla tylko jednego kanału (są dwa kanały, a więc mikrokontroler musi wysyłać próbki z częstotliwością dwukrotnie większą od częstotliwości próbkowania). Ponieważ jedno słowo wysyłane do przetwornika dla każdego z kanałów składa się z 24 bitów (16 bitów danych i bajt sterujący), łatwo policzyć, że konieczna do uzyskania przepływność danych wynosi:

2 kanały × 24 bity × 200kHz = 9,6Mb/s

Gdyby nie zastosowano DMA, procesor nie robiłby w zasadzie nic innego poza wysyłaniem kolejnych bajtów poprzez SPI i czekaniem na zakończenie transmsji. Dzięki DMA wystarczy przygotować bufor z danymi i uruchomić transmisję. Reszta dzieje się niejako „automatycznie” dzięki DMA i przerwaniu wywoływanemu po zakończeniu transmisji bufora w którym następuje przełączenie bufora i ustawienie flagi, oznaczającej konieczność załadowania nowego bufora. Dzięki temu zostało wystarczająco dużo czasu, aby obsłużyć kartę pamięci, przygotowywanie bufora danych oraz interfejs użytkownika.

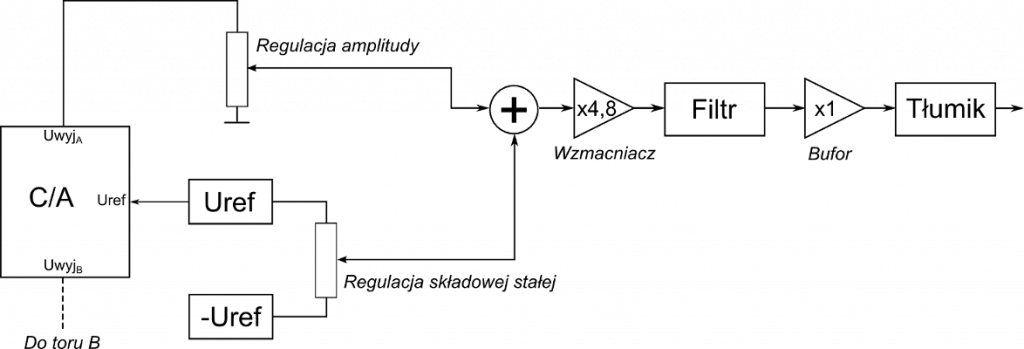

Część sygnałowa

Część sygnałowa układu składa się z układu regulacji amplitudy opisanego dalej oraz zestawu wzmacniaczy operacyjnych i filtru wyjściowego z tłumikami. Na poniższym rysunku przedstawiony został schemat blokowy tej części układu:

O ile układy wzmacniaczy oparte o wzmacniacze operacyjne raczej nie wymagają komentarza, to napiszę kilka słów o filtrze i tłumiku wyjściowym. Tłumik jest klasycznym tłumikiem typu T, umożliwiającym zachowanie impedancji wyjściowej równej 600Ω niezależnie od tego, czy jest włączony, czy nie. Jego tłumienie wynosi 20dB (czyli 10 razy). Zastosowany filtr jest prostym pasywnym filtrem drugiego rzędu z częstotliwością graniczną wynoszącą 70kHz. Gdybym obecnie projektował układ od nowa, na pewno zastosowałbym bardziej złożony filtr o bardziej stromej charakterystyce, lub nawet zestaw przełączanych filtrów.

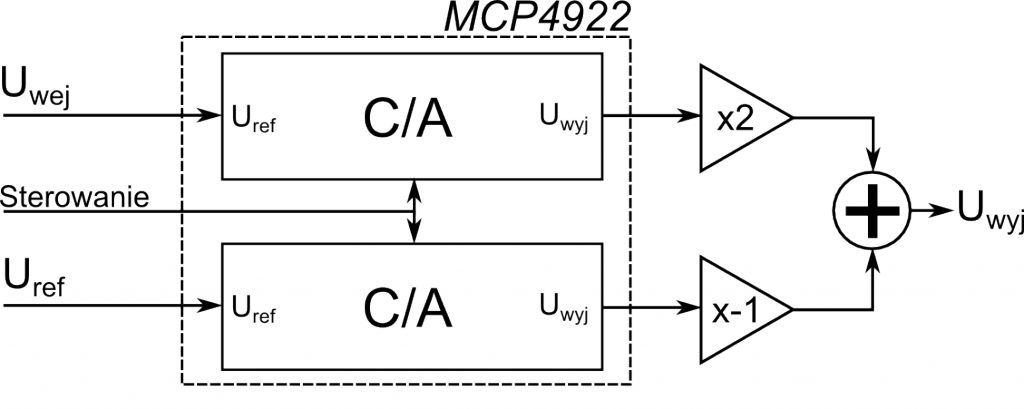

Układ regulacji amplitudy

Układ regulacji amplitudy jest dla mnie najbardziej „kontrowersyjną” częścią prezentowanego układu. Opiera się on o przetworniki MCP4922 i działa według koncepcji zaprezentowanej na poniższym schemacie blokowym.

Od razu muszę zaznaczyć, że układ ten działa źle, a przynajmniej nie tak dobrze, jak powinien. Jego złe działanie objawia się szczególnie w przypadku nastawienia niskiej amplitudy wyjściowej poprzez wprowadzanie znacznych zniekształceń widocznych podczas pomiarów THD, a nawet gołym okiem na oscyloskopie. Niestety, gdy podczas pomiarów zaobserwowałem problem i zlokalizowałem jego źródło, zostało już za mało czasu, by poprawiać układ. Gdybym obecnie projektował układ do regulacji amplitudy najpewniej zastosowałbym jedno z dwóch rozwiązań:

- Bipolarny potencjometr cyfrowy – tutaj prawdopodobnie pojawiłby się problem ze zdobyciem układu o zadowalającej rozdzielczości.

- Bipolarny mnożący przetwornik cyfrowo-analogowy.

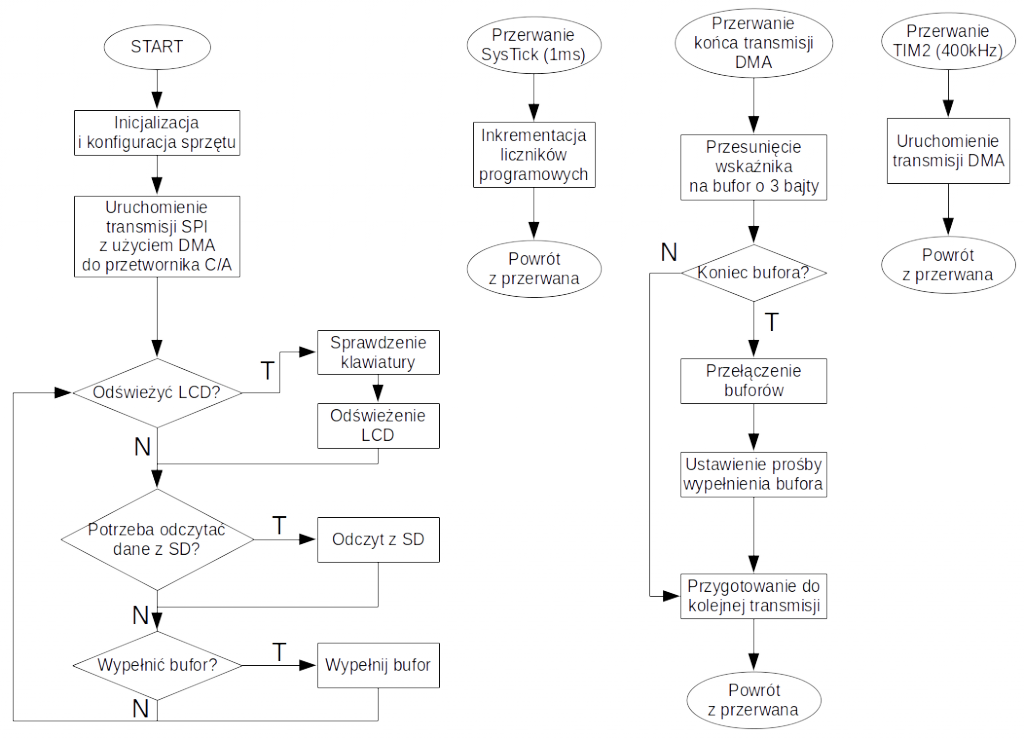

Program dla mikrokontrolera

Program dla mikrokontrolera powstał przy pomocy środowiska Eclipse i toolchaina GNU ARM Embedded. W niniejszym artykule nie będę dokładnie prezentował programu, gdyż jest on dosyć złożony i jego dokładny opis byłby bardzo długi. Nie opisuję również jego fragmentów, gdyż opisywanie takich wyrwanych z całości kawałków mijałoby się z celem. W zamian za to prezentuję poniżej schemat blokowy, przedstawiający ideę działania całego programu.

Pomiary THD

Podczas uruchamiania układu wykonany został pomiar THD, podczas którego zauważono nieporządane działanie układu regulacji amplitudy. W poniższej tabeli przedstawiłem wyniki pomiaru dla kolejno pełnej amplitudy, pełnej amplitudy z włączonym tłumikiem 20dB oraz amplitudy z tłumieniem 20dB uzyskanym przy pomocy układu regulacji ampitudy.

| Amplituda | 12V | 12V – 20dB | 1,2V |

| f[Hz] | THD[%] | THD[%] | THD[%] |

| 20 | 0,06 | 0,07 | 0,08 |

| 100 | 0,1 | 0,1 | 0,16 |

| 200 | 0,1 | 0,1 | 0,25 |

| 1k | 0,15 | 0,15 | 0,66 |

| 2k | 0,28 | 0,27 | 0,98 |

| 5k | 0,66 | 0,63 | 1,6 |

| 10k | 1,21 | 1,17 | 2,15 |

| 12k | 1,49 | 1,4 | 2,31 |

| 15k | 1,85 | 1,72 | 2,49 |

| 20k | 2,6 | 2,4 | 3 |

Podsumowanie i możliwości zmian

W wykonanym układzie udało się spełnić wszystkie założenia projektowe. Amplituda wyjściowa może wynosić maksymalnie 12V, a składowa stała może zawierać się w zakresie od -12V do 12V. Urządzenie obsługuje pliki w formacie WAV, szesnasto- lub ośmiobitowe, mono lub stereo. Próbkowanie pliku WAV może być dowolne, przy czym nie większe niż 200kHz. Jak pisałem już wcześniej, pomimo, że działa i spełnia swoje zadanie, nie jest to układ bez wad. Szczególnie do poprawy nadaje się układ regulacji amplitudy, oraz filtry wyjściowe. Można także pracować nad zwiększeniem częstotliwości próbkowania, jednakże pociągnie to za sobą zmianę przetwornika cyfrowo-analogowego oraz wymusi zastosowanie szybszego mikrokontrolera lub wykorzystanie układu FPGA, co znacznie skomplikuje cały układ.

Zdaję sobie sprawę, że układ jest opisany dosyć ogólnie, i jeżeli masz jakieś pytania to nie wahaj się ich zadawać – poprzez e-mail lub w komentarzu. Z chęcią na nie odpowiem.

Do pobrania

- Schematy układu – POBIERZ